Product Specification T2520-XV10T7-7600 Sep 2005

PMB 2520 Hammerhead A-GPS Single-Chip Device Confidential Distribution with NDA by marketing only

Short Range Wireless

Never stop thinking.

Edition 2005-09-29

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2005. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Product Specification T2520-XV10T7-7600 Sep 2005

## PMB 2520 Confidential Revision History:2005-09-29T2520-XV10T7-7600

Previous Version: T2520-XV10T5-7600

| Section/<br>Figure | Subjects (major changes since last revision) |

|--------------------|----------------------------------------------|

| Chapter1           | Added key performance figures                |

| Chapter 5          | Added interface timing                       |

| 1            | General Device Overview                             | . 8 |

|--------------|-----------------------------------------------------|-----|

| 1.1          | Key performance specification                       | 10  |

| 1.2          | System Architecture Overview                        | 12  |

| 1.3          | Pin Configuration PG-VQFN-48-4                      |     |

| 1.4          | Pin Description List (PG-VQFN-48-4)                 | 15  |

| 1.5          | System Overview                                     |     |

| 1.5.1        | RF frontend                                         | 18  |

| 1.5.1.1      | On-chip LNA                                         | 18  |

| 1.5.1.2      | I/Q mixers with pre-amplifier                       | 18  |

| 1.5.1.3      | Polyphase complex filter                            |     |

| 1.5.1.4      | Digitally controlled AGC with power level detection | 19  |

| 1.5.1.5      | 3-bit A/D converters for I and Q paths              | 19  |

| 1.5.1.6      | Local oscillator and PLL                            | 19  |

| 1.5.1.7      | Voltage regulator                                   | 19  |

| 1.5.1.8      | Baseband interface                                  | 19  |

| 1.5.2        | GPS Baseband                                        | 20  |

| 1.5.3        | Host software                                       |     |

| 1.5.3.1      | Host software Architecture                          | 21  |

| 1.5.4        | Test interface                                      | 22  |

| 1.6          | System Integration                                  | 22  |

| 2            | Host Interfaces                                     | 2.6 |

| 2.1          | UART Host Interface                                 |     |

| 2.1.1        | Baud Rate Generator                                 |     |

| 2.1.2        | Asynchronous Receiver                               |     |

| 2.1.3        | Receiver Flow Control                               |     |

| 2.1.4        | Asynchronous Transmitter                            |     |

| 2.1.5        | Transmitter Flow Control                            |     |

| 2.1.6        | UART Chip Select                                    |     |

| 2.2          | SPI Host Interface                                  |     |

| 2.2.1        | SPI Cycles                                          |     |

| 2.3          | I <sup>2</sup> C Host Interface                     |     |

| 2.3.1        | I <sup>2</sup> C Slave Address                      |     |

| 2.3.2        | I2C Read/Write Cycles                               |     |

| 2.4          | Status, Control, and Data Registers                 |     |

| 2.5          | nINTR                                               |     |

| 2.5.1        | I2C and SPI                                         | 38  |

| 2.5.2        | UART                                                |     |

| 3            | System Clocks description                           | 10  |

| 3.1          | Overview                                            |     |

| 3.2          | Reference clock                                     |     |

|              |                                                     |     |

| 391          |                                                     |     |

| 3.2.1<br>3.3 | UART, SPI and I2C interfaces                        | 40  |

| 3.4<br>3.5 | CNTIN clock                                            |    |

|------------|--------------------------------------------------------|----|

| 4          |                                                        |    |

| 4<br>4.1   | Power Management                                       |    |

| 4.1.1      | Internal voltage regulators.                           |    |

|            |                                                        |    |

| 4.1.2      | External regulated voltage supplies.                   |    |

| 4.1.5      | A combination of the above.                            |    |

|            | Power Up and Power Down Sequencing                     |    |

| 4.2.1      | Power Up Sequence                                      | 44 |

| 4.2.2      | Power Down Sequence                                    |    |

| 4.3        | Power Modes                                            |    |

| 4.3.1      | Full Processing Mode                                   |    |

| 4.3.2      | Reduced Processing Mode                                |    |

| 4.3.3      | Software Only Standby                                  |    |

| 4.3.4      | Low Power Standby                                      |    |

| 4.3.5      | Power Down                                             |    |

| 4.3.6      | IC Off                                                 | 49 |

| 5          | Electrical Characteristics                             | 51 |

| 5.1        | Absolute Maximum Ratings                               | 51 |

| 5.2        | Operating Ranges                                       | 52 |

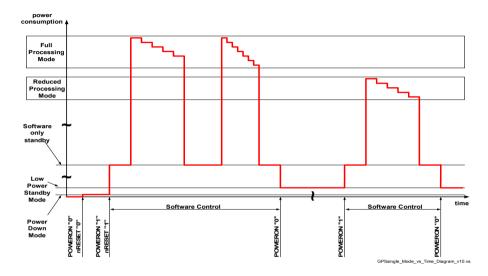

| 5.3        | DC Characteristics                                     | 53 |

| 5.3.1      | DC characteristic Digital I/O Pads                     | 53 |

| 5.3.2      | DC characteristic I2C Pads (I2C SCL, I2C SDA)          | 54 |

| 5.3.3      | Pull-Up and Pull-Down Values of JTAG interface         |    |

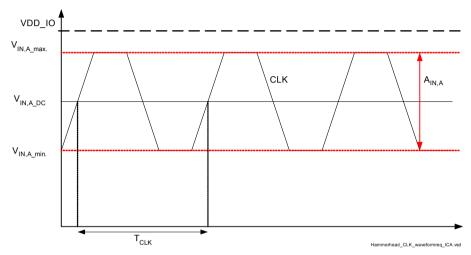

| 5.4        | CLK Input Clock Amplifier (ICA) characteristics        | 56 |

| 5.5        | Current Consumption                                    |    |

| 5.5.1      | Internal Digital Power Consumption                     |    |

| 5.5.2      | Internal RF Power Consumption                          |    |

| 5.6        | Current Consumption of Different Voltage Domains       |    |

| 5.6.1      | Typical Current Consumption of Digital Voltage Domains |    |

| 5.6.2      | Internal Current Consumption of Digital Regulators     |    |

| 5.7        | Regulator Characteristics                              |    |

| 5.7.1      | Regulator Limits(DC)                                   |    |

| 5.7.2      | Regulator Limits (Dynamic)                             |    |

| 5.8        | RF parameters                                          |    |

| 5.8.1      | Noise performance                                      |    |

| 5.8.2      | Internal LNA                                           |    |

| 5.8.3      | 2nd LNA, Mixer and IF filter.                          |    |

| 5.8.4      | PGC amplifier                                          |    |

| 5.9        | AC Characteristics                                     |    |

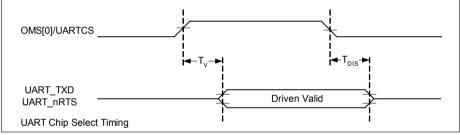

| 5.9.1      | UART Chip Select Timing                                |    |

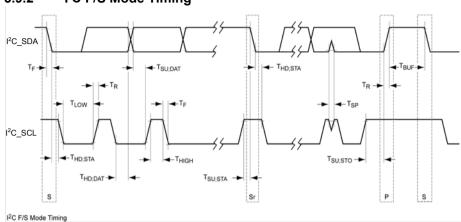

| 5.9.2      | I2C F/S Mode Timing                                    |    |

| Package footprint69Links to more information70Appendix A Package and handling71Storage, baking and handling71ESD sensitivity71Moisture Sensitivity Level71Peak package temperature level71 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Links to more information       70         Appendix A Package and handling       71         Storage, baking and handling       71         ESD sensitivity       71                         |

| Links to more information       70         Appendix A Package and handling       71         Storage, baking and handling       71                                                          |

| Links to more information    70      Appendix A Package and handling    71                                                                                                                 |

| Links to more information                                                                                                                                                                  |

|                                                                                                                                                                                            |

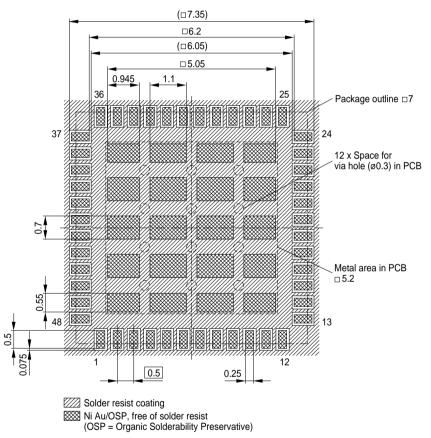

| Package footprint                                                                                                                                                                          |

|                                                                                                                                                                                            |

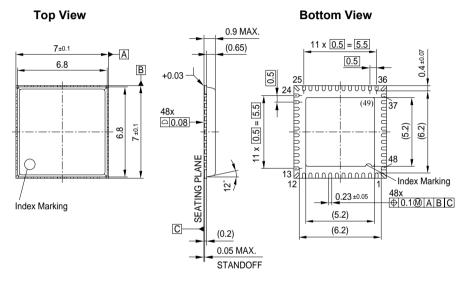

| Package Outline                                                                                                                                                                            |

| Package                                                                                                                                                                                    |

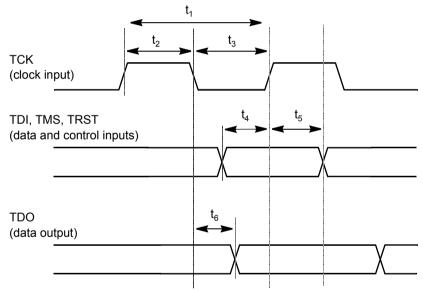

| Boundary Scan Timing                                                                                                                                                                       |

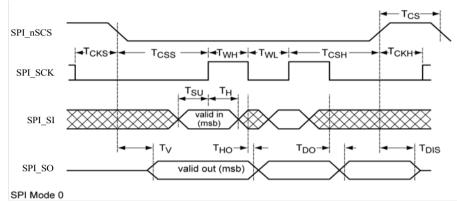

| SPI Mode timing                                                                                                                                                                            |

|                                                                                                                                                                                            |

**General Device Overview**

# 1 General Device Overview

The PMB 2520 Hammerhead GPS IC is Infineon Technologies and Global Locate's next generation IC solution for GPS (Global Positioning System). The Hammerhead GPS single chip device enables the realization of a cost efficient GPS solution by integrating the complete radio frequency front-end as well as the signal processing functionality in a single die. The radio frequency front-end includes an LNA (low noise amplifier), VCO (voltage controlled oscillator), PLL (phase locked loop) and analog to digital converters. The PMB 2520 Hammerhead IC allows the usage of assistance data by supporting A-GPS (assisted GPS) standards (RRLP, RRC, OMA SUPL).

With the help of advanced digital signal processing techniques based on sophisticated correlation engines as well as powerful detection and navigation processing algorithms and the use of A-GPS data, the Hammerhead achieves enhanced sensitivity values of better than -158 dBm at the LNA input as is required for indoor applications. A sophisticated dynamic power management scheme supports several low-power modes which gives the lowest possible energy usage per fix.

The Hammerhead is especially targeted at the cellular market but it can also be used for automotive navigation and infotainment systems as well as the wireless PDA market segment. The main applications for Hammerhead are location based services and the localization of emergency calls for cellular systems according to, for example, the E911 mandate. In conjunction with the appropriate software and driver, integrated on the cellular host, the Hammerhead system realizes the complete functionality for mobile-assisted, mobile-based and/or autonomous GPS operation. By integrating the signal processing functionality the host system is relieved of all real-time critical A-GPS tasks.

One of three serial interfaces, UART, I<sup>2</sup>C or SPI, is used for communication with the host system. A JTAG interface for boundary scan is also available.

The device is fabricated in advanced semiconductor technology and is available in a PG-VQFN-48-4 package.

# A-GPS Single Chip Device

Global

## PMB 2520

## Feature Overview

#### General

- Single-chip A-GPS device for cellular applications and location based services, integrating the radio frontend and the GPS baseband on the same die

- Fabricated in advanced low-power 0.13µm CMOS technology

- Low power consumption using several power saving modes

- Supply from external voltage regulators or use the built in voltage regulators

- Advanced real time hardware correlator engine for enhanced sensitivity (better than -158 dBm at the LNA input for A-GPS)

- Fast Acquisition giving rapid Time-to-First-Fix (TTFF)

- Very low component count for lowest bill of material

- Multiple input clock signals supported

- · Range of interface voltages supported

- Temperature range of -30°C to +85°C

## Interfaces

- RF antenna input

- Serial full duplex UART interface

- Serial I<sup>2</sup>C interface

- · Serial full-duplex synchronous SPI interface

- IEEE 1149.1 compatible JTAG Test Access Port (TAP) and boundary scan

#### Software

- Hammerhead host software driver supports multiple mode operation (mobile-assisted, mobile-based and autonomous).

- · Easy to use driver API

| Туре                  |       | Package                       |

|-----------------------|-------|-------------------------------|

| PMB 2520              | PG-VQ | FN-48-4                       |

| Product Specification | 9     | T2520-XV10T7-7600, 2005-09-29 |

General Device Overview

#### 1.1 Key performance specification

The specifications in this section are intended to provide guidance regarding typical system performance for cellular handsets utilizing the PMB 2520 Hammerhead. The achievable performance for a particular handset will vary depending upon RF environment and implementation.

The PMB2520 Hammerhead is designed to operate in networks without GPS timing, using approximate time provided through assistance data messages. The specifications below are inclusive of any degradations induced from timing errors of two seconds.

#### Table 1-1 Accuracy

| Signal condition for all | Circular Error Probability (CEP) accuracy |                       |  |  |  |  |  |

|--------------------------|-------------------------------------------|-----------------------|--|--|--|--|--|

| satellites               | First Fix                                 | Continuous Navigation |  |  |  |  |  |

| -130 dBm                 | 10 m                                      | 2 m (note 1)          |  |  |  |  |  |

| -150 dBm                 | 20 m                                      | 10 m                  |  |  |  |  |  |

| -160 dBm                 | 100 m (note 2)                            | 50 m                  |  |  |  |  |  |

Notes:

1. Atmospheric effects may degrade outdoor accuracy to 5m.

2. One satellite at -147dBm.

#### Table 1-2 Sensitivity

| Type of fix                         | Minimum signal strength (signal condition for all Satellites) |

|-------------------------------------|---------------------------------------------------------------|

| Hot start (first fix after standby) | -160 dBm                                                      |

| First fix (MS-based or MS-assisted) | -154 dBm                                                      |

| First fix (Enhanced Autonomous)     | -150 dBm                                                      |

| First fix (Autonomous)              | -140 dBm                                                      |

#### Table 1-3 Average power consumption

| Signal condition for all satellites |            |

|-------------------------------------|------------|

| -130 dBm                            | 70mW       |

| -150 dBm                            | 100mW      |

| -130 dBm                            | 25mW(note) |

| Note:                               |            |

Low-power mode = 1Hz update rate with measurement time of 200ms

**General Device Overview**

## Confidential

## Table 1-4Time To First Fix

| Signal condition   | Time to first fix                      |                                            |                           |                                       |  |  |  |  |  |  |  |

|--------------------|----------------------------------------|--------------------------------------------|---------------------------|---------------------------------------|--|--|--|--|--|--|--|

| for all satellites | Hot start<br>(First Fix After Standby) | First Fix<br>(Ms-based or MS-<br>assisted) | First Fix<br>(Autonomous) | First Fix<br>(Enhanced<br>Autonomous) |  |  |  |  |  |  |  |

| -130 dBm           | 1 s                                    | 1 s                                        | 60 s                      | 15 s (note 1)                         |  |  |  |  |  |  |  |

| -140 dBm           | 2 s                                    | 2 s                                        | 60 s                      |                                       |  |  |  |  |  |  |  |

| -150 dBm           | 6 s                                    | 10 s                                       | -                         | 30 s                                  |  |  |  |  |  |  |  |

| -160 dBm           | < 60 s                                 | < 60 s<br>(note 2)                         | -                         | -                                     |  |  |  |  |  |  |  |

Notes:

1. Enhanced Autonomous operation uses Global Locate's proprietary LTO file.

2. One satellite at -147dBm.

**General Device Overview**

# 1.2 System Architecture Overview

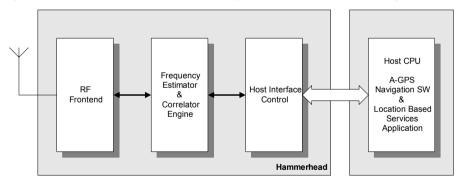

**Figure 1-1** shows a coarse block diagram of the complete GPS system architecture consisting of the PMB 2520 Hammerhead GPS IC and the host CPU. The Hammerhead is targeted mainly at cellular application like Location Based Services and the localization of emergency calls for cellular systems according to, for example, the E911 mandate. All the real-time critical signal processing for A-GPS operation is performed internally in the Hammerhead, removing any real-time loading from the system host CPU.

The corresponding host software allows for the operation of mobile-assisted and mobilebased A-GPS fully autonomous GPS and / or Global Locate patented Enhanced Autonomous. A flexible API (<u>Application Programming Interface</u>) is provided with the navigation software allowing an easy integration of the A-GPS functionality into e.g. a cellular protocol stack. No real-time interrupt service loading is added to the host system, thus considerably simplifying the system integration.

To support debug and production tests the PMB 2520 Hammerhead GPS IC contains a TAP controller. The TAP controller is compatible with the IEEE Standard Test Access and Boundary-Scan Architecture, IEEE Std 1149.1-2001.

### Figure 1-1 Hammerhead GPS Coarse System Architecture including Host CPU

GPSsingle\_Coarse\_System\_Overview\_v10.vsd

#### **General Device Overview**

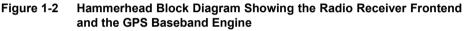

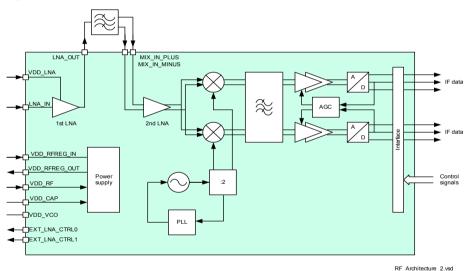

A more detailed system diagram showing the modules integrated in the Hammerhead as well as an external SAW (surface acoustic wave) filter is shown in **Figure 1-2**. The Hammerhead consists of the following modules:

- RF front-end with on-chip, high gain and low noise, LNA, I/Q mixers, on-chip polyphase complex IF filter, digitally controlled AGC, and 3-bit ADC for the I and Q paths

- · Sigma-Delta RF PLL with on-chip VCO and on-chip loop filter

- · Embedded PLL and NCO for baseband clock generation

- 8 channels digital mixers and massive parallel correlator engines to enable real time correlation of the PRN code

- · Post processor including peak detection logic

- SRAM for storing correlation results

**General Device Overview**

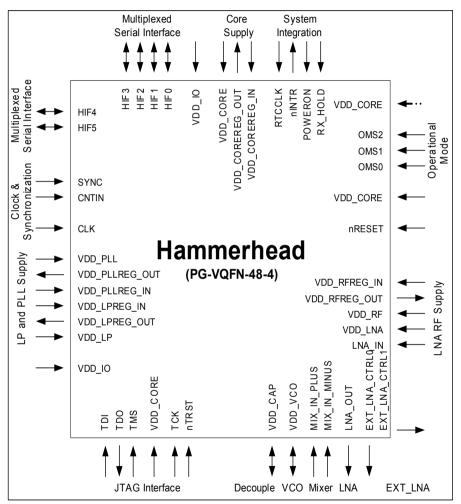

# 1.3 Pin Configuration PG-VQFN-48-4

#### Figure 1-3 Logic Symbol of the Hammerhead (PG-VQFN-48-4) PMB 2520

GPSsingle\_logic\_symbol\_vqfn\_external\_v10.vsd

**General Device Overview**

# 1.4 Pin Description List (PG-VQFN-48-4)

### Table 1-5 Pin List of Hammerhead (PG-VQFN-48-4)

| Pin<br>No. | Pin<br>Name        | Pad<br>Type |           | ad<br>age  | O/P<br>State |         |                                                                      |

|------------|--------------------|-------------|-----------|------------|--------------|---------|----------------------------------------------------------------------|

|            |                    |             | Direction | Additional | Reset        | Standby | Pad Functional Description                                           |

| 1          | TDI                | I/O         | I         | PU "C"     | 1            | 1       | Serial Data Input (JTAG, IEEE 1149.1)                                |

| 2          | TDO                | I/O         | 0         | -          | Z            | Z       | Serial Data Output (JTAG, IEEE 1149.1)                               |

| 3          | тмѕ                | I/O         | I         | PU "C"     | 1            | 1       | State Machine Control Signal (JTAG, IEEE 1149.1)                     |

| 4          | VDD_CORE           | PI          | -         | -          | -            | -       | Digital core supply                                                  |

| 5          | тск                | I/O         | I         | PD "C"     | 0            | 0       | Clock (JTAG, IEEE 1149.1)                                            |

| 6          | nTRST              | I/O         | I         | PD "A"     | 0            | 0       | Reset Input (JTAG, IEEE 1149.1)                                      |

| 7          | VDD_CAP            | AI/O        | AI/O      | -          | (Z)          | (Z)     | RF Digital Supply Decoupling                                         |

| 8          | VDD_VCO            | AI/O        | AI/O      | -          | (Z)          | (Z)     | Buffer capacitor for VCO supply                                      |

| 9          | MIX_IN_PLUS        | AI          | AI        | -          | -            | -       | Differential mixer input                                             |

| 10         | MIX_IN_MINUS       | AI          | AI        | -          | -            | -       | Differential mixer input                                             |

| 11         | LNA_OUT            | AO          | AO        | -          | -            | -       | LNA output signal                                                    |

| 12         | EXT_LNA_CTRL0      | AI/O        | 0         | -          | -            | -       | External LNA control                                                 |

| 13         | EXT_LNA_CTRL1      | AI/O        | 0         | -          | -            | -       | External LNA control                                                 |

| 14         | LNA_IN             | AI          | AI        | -          | -            | -       | LNA input signal                                                     |

| 15         | VDD_LNA            | PI          | -         | -          | -            | -       | LNA supply voltage                                                   |

| 16         | VDD_RF             | PI          | -         | -          | -            | -       | IF RF circuit supply voltage                                         |

| 17         | VDD_RFREG_OU<br>T  | PO          | -         | -          | -            | -       | RF voltage regulator output                                          |

| 18         | VDD_RFREG_IN       | PI          | -         | -          | -            | -       | RF voltage regulator input                                           |

| 19         | nRESET             | I/O         | I         | Hyst       | 0            | 1       | Chip reset signal                                                    |

| 20         | VDD_CORE           | PI          | -         | -          | -            | -       | Digital core supply                                                  |

| 21         | OMS0               | I/O         | I         | -          | -            | -       | Operational mode select / Bus interface select                       |

| 22         | OMS1               | I/O         | I         | -          | -            | -       | Operational mode select / Bus interface select                       |

| 23         | OMS2               | I/O         | I         | -          | -            | -       | Operational mode select                                              |

| 24         | VDD_CORE           | PI          | -         | -          | -            | -       | Digital core supply                                                  |

| 25         | RX_HOLD            | I/O         | I         | -          | -            | -       | RX_HOLD signal (From host to indicate that the host is transmitting) |

| 26         | POWERON            | I/O         | I         | -          | 0            | 0       | Power On signal to chip                                              |

| 27         | nINTR              | I/O         | 0         | OD         | Z            | Z       | Interrupt request signal to host                                     |

| 28         | RTCCLK             | I/O         | I         | Hyst       | -            | -       | 32.768kHz clock signal input                                         |

|            | VDD_COREREG_I<br>N | PI          | -         | -          | -            | -       | Digital core voltage regulator supply                                |

## Confidential

### **General Device Overview**

## Table 1-5Pin List of Hammerhead (PG-VQFN-48-4) (cont'd)

| Pin<br>No. | Pin<br>Name                                                  | Pad<br>Type |                           | ad<br>age         | O/P<br>State     |                  |                                                                                                                                                                                                                                                                       |

|------------|--------------------------------------------------------------|-------------|---------------------------|-------------------|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                                              |             | Direction                 | Additional        | Reset            | Standby          | Pad Functional Description                                                                                                                                                                                                                                            |

|            | VDD_COREREG_<br>OUT                                          | PO          | -                         | -                 | -                | -                | Digital core voltage regulator output                                                                                                                                                                                                                                 |

| 31         | VDD_CORE                                                     | PI          | -                         | -                 | -                | -                | Digital core supply                                                                                                                                                                                                                                                   |

| 32         | VDD_IO                                                       | PI          | -                         | -                 | -                | -                | Digital I/O supply                                                                                                                                                                                                                                                    |

|            | HIF0<br>- /<br>- /<br>I <sup>2</sup> C_SCL /<br>-            | I/O         | <br> <br> ²C  <br>        | -                 | -<br>-<br>-      | -<br>-<br>-      | Host Interface<br>OMS[2:0]=[1,1,1]: not used (tie to "0")<br>OMS[2:0]=[1,1,0]: not used (tie to "0")<br>OMS[2:0]=[1,0,1]: I <sup>2</sup> C clock<br>OMS[2:0]=[1,0,0]: not used (tie to "0")                                                                           |

|            | -                                                            |             | -                         | -                 | -                | -                | OMS[2:0]=[0,x,x]: Reserved, Do not use.                                                                                                                                                                                                                               |

|            | HIF1<br>- /<br>- /<br>I²C_SDA /<br>-                         | I/O         | <br> <br> ²C  /O<br>      | -<br>-<br>OD<br>- | -<br>-<br>Z<br>- | -<br>-<br>Z<br>- | Host Interface<br>OMS[2:0]=[1,1,1]: not used (tie to "0")<br>OMS[2:0]=[1,1,0]: not used (tie to "0")<br>OMS[2:0]=[1,0,1]: I <sup>2</sup> C data<br>OMS[2:0]=[1,0,0]: not used (tie to "0")                                                                            |

|            | -                                                            |             | -                         | -                 | -                | -                | OMS[2:0]=[0,x,x]: Reserved, Do not use.                                                                                                                                                                                                                               |

|            | HIF2<br>UART_TXD /<br>UART_TXD /<br>I²C_GROUP0 /<br>SPI_SCK  | I/O         | O<br>Z<br>I<br>I          | -<br>-<br>-       | 0<br>Z<br>-      | 0<br>Z<br>-      | Host Interface<br>OMS[2:0]=[1,1,1]: UART Interface: Data Output<br>OMS[2:0]=[1,1,0]: UART Interface: Data Output (Tristated)<br>OMS[2:0]=[1,0,1]: Selection of I <sup>2</sup> C group address<br>OMS[2:0]=[1,0,0]: SPI clock                                          |

|            | -                                                            |             | -                         | -                 | -                | -                | OMS[2:0]=[0,x,x]: Reserved, Do not use.                                                                                                                                                                                                                               |

|            | HIF3<br>UART_RXD /<br>UART_RXD /<br>I²C_GROUP1 /<br>SPI_nSCS | I/O         | <br>(l)<br> <br>          | -<br>-<br>-       | -<br>-<br>-      | -<br>-<br>-      | Host Interface<br>OMS[2:0]=[1,1,1]: UART Interface: Data Input<br>OMS[2:0]=[1,1,0]: UART Interface: Data Input (Ignored)<br>OMS[2:0]=[1,0,1]: Selection of I <sup>2</sup> C group address<br>OMS[2:0]=[1,0,0]: SPI chip select                                        |

|            | -                                                            |             | -                         | -                 | -                | -                | OMS[2:0]=[0,x,x]: Reserved, Do not use.                                                                                                                                                                                                                               |

|            | HIF4<br>UART_nRTS /<br>UART_nRTS /<br>I²C_A0 /<br>SPI_SI     | I/O         | O<br>Z<br>I<br>I          | -<br>-<br>-       | 0<br>Z<br>-      | 0<br>Z<br>-      | Host Interface<br>OMS[2:0]=[1,1,1]: UART Interface: hardware flow control<br>OMS[2:0]=[1,1,0]: UART Interface: hardware flow control<br>(Tristated)<br>OMS[2:0]=[1,0,1]: Selection of I <sup>2</sup> C group address bit 0<br>OMS[2:0]=[1,0,0]: SPI serial data input |

|            | -                                                            |             | -                         | -                 | -                | -                | OMS[2:0]=[0,x,x]: Reserved, Do not use.                                                                                                                                                                                                                               |

|            | HIF5<br>UART_nCTS /<br>UART_nCTS /<br>- /<br>SPI_SO          | I/O         | -<br> <br>(l)<br> <br>O/Z | -<br>-<br>-       | -<br>-<br>-<br>Z | -<br>-<br>-<br>Z | Host Interface<br>OMS[2:0]=[1,1,1]: UART Interface: hardware flow control<br>OMS[2:0]=[1,1,0]: UART Interface: hardware flow control<br>(Ignored)<br>OMS[2:0]=[1,0,1]: not used (tie to "0")<br>OMS[2:0]=[1,0,0]: SPI serial data output                              |

|            | -                                                            |             | -                         | -                 | -                | -                | OMS[2:0]=[0,x,x]: Reserved, Do not use.                                                                                                                                                                                                                               |

## Confidential

## **General Device Overview**

## Table 1-5 Pin List of Hammerhead (PG-VQFN-48-4) (cont'd)

| Pin<br>No. | Pin<br>Name        | Pad<br>Type | Pad O/P<br>Usage State |            |       |         |                                                           |

|------------|--------------------|-------------|------------------------|------------|-------|---------|-----------------------------------------------------------|

|            |                    |             | Direction              | Additional | Reset | Standby | Pad Functional Description                                |

| 39         | SYNC               | I           | I                      | -          | -     | -       | Digital reference time pulse                              |

| 40         | CNTIN              | I           | I                      | -          | -     | -       | Digital high accuracy frequency reference                 |

| 41         | CLK                | I/AI        | I                      | -          | -     | -       | Clock signal input. Selectable as digital or analog input |

| 42         | VDD_PLL            | PI          | -                      | -          | -     | -       | Digital PLL supply                                        |

|            | VDD_PLLREG_O<br>UT | PO          | -                      | -          | -     | -       | PLL voltage regulator output                              |

| 44         | VDD_PLLREG_IN      | PI          | -                      | -          | -     | -       | PLL voltage regulator input                               |

| 45         | VDD_LPREG_IN       | PI          | -                      | -          | -     | -       | Low Power core regulator input                            |

| 46         | VDD_LPREG_OU<br>T  | PO          | -                      | -          | -     | -       | Low Power core regulator output                           |

| 47         | VDD_LP             | PI          | -                      | -          | -     | -       | Low Power supply                                          |

| 48         | VDD_IO             | PI          | -                      | -          | -     | -       | Digital I/O supply                                        |

| (49<br>)   | VSS                | GND         | -                      | -          | -     | -       | Ground Pad. This is the exposed pad of the package        |

### Table 1-6 Key to Table 1-5

| Pad Type | Description           | Comments                                                                                                                                                                                                                                                               |

|----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND      | Chip Ground           | All signals are referred to this                                                                                                                                                                                                                                       |

| PI       | Power In              | Supply to a voltage domain                                                                                                                                                                                                                                             |

| PO       | Power Out             | Regulator Output                                                                                                                                                                                                                                                       |

| 1/0      | Pad                   | All Digital Pads are I/O Pads which are configured internally as required.<br>- All are configured as Push-Pull except those marked as OD (open drain)<br>- All have hysteresis by default, but is only mentioned when it is required for correct<br>system operation. |

| AI       | Analog Input          |                                                                                                                                                                                                                                                                        |

| AO       | Analog Output         |                                                                                                                                                                                                                                                                        |

| PU       | Internal Pull Up      | See Table 5-5 for definition of drive strengths "A" and "C".                                                                                                                                                                                                           |

| PD       | Internal Pull<br>Down | See Table 5-5 for definition of drive strengths "A" and "C".                                                                                                                                                                                                           |

## Confidential

**General Device Overview**

## 1.5 System Overview

## 1.5.1 RF frontend

The RF front-end integrates the following components:

- On-chip LNA

- I/Q mixers with pre-amplifier

- · Polyphase complex IF filter

- · Digitally controlled AGC with power level detection

- · 3-bit A/D converters for I and Q paths

- · Local Oscillator and PLL

- · Voltage regulator

#### Figure 1-4 RF frontend block overview

## 1.5.1.1 On-chip LNA

The on-chip LNA is optimized to achieve high gain accompanied by a low noise figure and acceptable blocking performance.

## 1.5.1.2 I/Q mixers with pre-amplifier

The pre-amplifier has differential inputs, and the LNA gain is selectable. The mixers convert the RF to an IF signal.

## Confidential

#### **General Device Overview**

## 1.5.1.3 Polyphase complex filter

The polyphase complex filter contains a low noise amplifier and a complex IF filter.

## 1.5.1.4 Digitally controlled AGC with power level detection

Following the complex bandpass filter an AGC, containing digitally controlled PGC IF amplifiers and a gain adjustment loop, will adjust the signal to a level suitable for the A to D converters. The PGC gain adjustment range is designed to handle a maximum of 16dB added external gain in addition to the 1st LNA.

## 1.5.1.5 3-bit A/D converters for I and Q paths

The AD converters digitize the I and Q signals for the baseband processing.

## 1.5.1.6 Local oscillator and PLL

The local oscillator and PLL generate the  $0^{\circ}$  and  $90^{\circ}$  phase shifted signals for the I-/Qmixers. The VCO contains an automatic VCO trim procedure to trim the frequency to the intended one using the RF\_CLK as reference.

## 1.5.1.7 Voltage regulator

The RF frontend contains a voltage regulator optimized to supply the RF frontend and the LNA.

## 1.5.1.8 Baseband interface

The RF front-end interfaces to the baseband subsystem via a tailored BB/RF interface and several control and configuration registers which control the operation of the RF front-end.

#### **General Device Overview**

## 1.5.2 GPS Baseband

The GPS baseband implements a 8 channel digital GPS receiver each integrating the following components:

- Complex digital 4-quadrant mixer with a numerically controlled oscillator (NCO) signal generation

- Correlator processor with parallel correlator engines, PRN code generation and post correlation processor

- · Correlation results SRAM with peak detection logic

The serial host interface can be configured, using the OMS pins, to one of the following interface types.

- UART

- I<sup>2</sup>C

- SPI

A clock PLL in the baseband generates the required internal clock signals from an external reference clock. Additionally a 32.768kHz clock signal is required. This 32.768kHz is also used for specific low-power modes.

## Confidential

#### **General Device Overview**

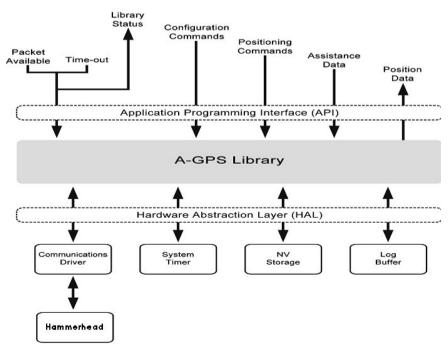

## 1.5.3 Host software

The Hammerhead system described in **Figure 1-1**shows the whole system including the mandatory software on the host. This software is required to configure and control the hammerhead chip, i.e. it is the software driver.

The host software is supplied with the hammerhead chip and is easily integrated on the host.

## 1.5.3.1 Host software Architecture

The Hammerhead driver software is delivered as a library specifically configured for the customer needs. The library has two dedicated interfaces for the host application software, see **Figure 1-5**. The "upper" part is the API that contains functionality used by the GPS navigation software presenting the location to the user. The "lower" API is the HAL (Hardware Abstraction Layer), interfacing the host system resources such as OS functions. The HAL needs to be adapted to the hardware and OS used in the host system.

#### Figure 1-5 Software Architecture

Product Specification

#### **General Device Overview**

## Confidential

## 1.5.4 Test interface

A JTAG interface is integrated for test purposes and to allow boundary scan.

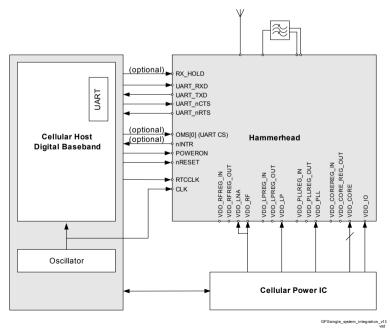

# 1.6 System Integration

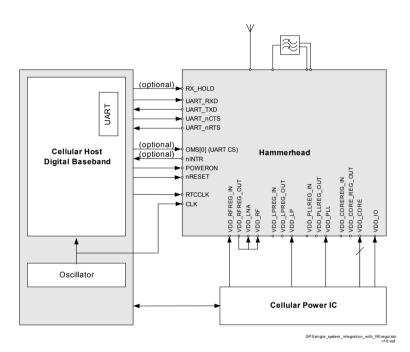

In **Figure 1-6**, **Figure 1-7**, **Figure 1-8** and **Figure 1-9** the integration of the PMB 2520 Hammerhead A-GPS IC into a cellular host system is shown. **Figure 1-6** shows a system configuration in which the reference clock is provided by the cellular host system. The RF and digital voltages are supplied from the system power supply device using neither the internal RF voltage regulator, the VDD\_Core voltage regulator, the PLL voltage regulator nor the Low Power voltage regulator.

A reference clock is provided by the host system. Additionally a 32.768kHz clock signal (RTCCLK) is required. This 32.768kHz is also used for specific low-power modes.

To switch the Hammerhead into and out of low-power modes the signal POWERON is provided.

#### Figure 1-6 Hammerhead Integration into a Host System connected by a Serial Interface without using any of the internal voltage regulators. (Example shows the UART as the serial interface).

Product Specification

## Confidential

#### **General Device Overview**

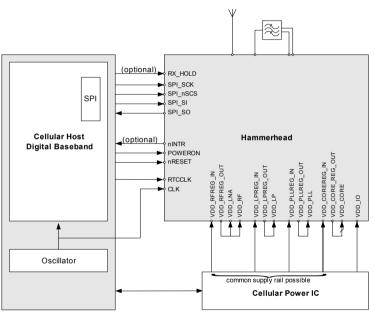

In **Figure 1-7** a system configuration is shown similar to the one in **Figure 1-6** but with the internal RF voltage regulator used.

#### Figure 1-7 Hammerhead Integration into a Host System connected by a Serial Interface using the internal RF voltage regulator. (Example shows the UART as the serial interface).

## Confidential

#### **General Device Overview**

In **Figure 1-8** a system configuration is shown in which all the internal voltage regulators and the SPI interface is used.

#### Figure 1-8 Hammerhead Integration into a Host System connected by a Serial Interface using all the internal voltage regulators. (Example shows the SPI as the serial interface).

GPSsingle\_system\_integration\_using\_regulators\_v 10.vsd

#### **General Device Overview**

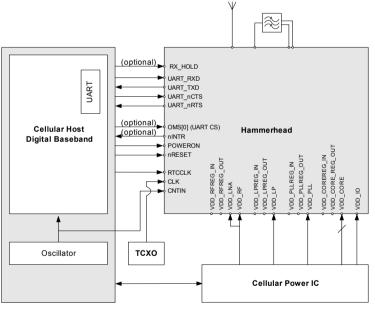

In **Figure 1-9** a system configuration is shown in which the reference clock is provided by an external temperature-controlled crystal oscillator.

With the help of the signal CNTIN the cellular clock may be provided by the cellular system for calibration and synchronization purposes.

Figure 1-9 Hammerhead Integration into a Host System connected by a Serial Interface with external TCXO and additional Frequency Reference provided by the Cellular Host and without using the internal voltage regulators.

(Example shows the UART as the serial interface).

GPSsingle\_system\_integration\_with\_TCXC v10.vsd

# Confidential

#### Host Interfaces

# 2 Host Interfaces

The Hammerhead integrates 3 serial interfaces:

- UART Universal Asynchronous Receiver / Transmitter

- I<sup>2</sup>C bus Inter-IC bus

- SPI <u>Serial Peripheral Interface</u>

Since only one interface can be active in any specific system integration scenario, the interface signals are multiplexed onto the same pins. The exception being the  $I^2C\_SCL$  and  $I^2C\_SDA$  signals which are kept separate as the  $I^2C$  switching levels on these pins are different. See **Table 1-5** for the pin list. Which interface is used in any particular application is selected by the OMS[2:0] pins according to the following **Table 2-1**.

Table 2-1 Host Interface Selection by OMS[2:0]

| Host Interface | UART | UART(Disabled) | l²C | SPI |

|----------------|------|----------------|-----|-----|

| OMS[2]         | 1    | 1              | 1   | 1   |

| OMS[1]         | 1    | 1              | 0   | 0   |

| OMS[0]         | 1    | 0              | 1   | 0   |

In the following sections the interfaces together with the relevant status, control and data registers are described.

Note: As the UART INTERFACE may be bussed, the state OMS[110] disables the UART interface and puts the UART outputs from the Hammerhead (UART\_TXD and UART\_nRTS) into tri-state mode. See Chapter 2.1.6

## Confidential

#### Host Interfaces

# 2.1 UART Host Interface

The Hammerhead provides a full-duplex UART (Universal Asynchronous Receiver Transmitter) interface which can be used to interface to an external host. The UART interface comprises the following features:

- Contains an NCO-based baud rate generator that enables generation of any baud rate from 1/4095<sup>th</sup> up to 1/32<sup>nd</sup> of the supplied reference clock frequency, and allows more flexibility than a simple integer divider.

- Automatic baud rate matching after reset.

- Programmable transmit pacing allows the Hammerhead UART transmit rate to be reduced without reducing the baud rate. This is achieved by inserting a configurable number of idle bits between transmitted characters, see **Table 2-2**. This reduced transfer rate relaxes the demands on the host UART receive path without impeding the host UART transmit rate.

- Supports hardware flow control through the use of nCTS (clear to send) and nRTS (ready for receiving) pins.

- 18-byte receiver FIFO enables the Hammerhead UART to be connected to an external UART without hardware flow control. (Software on the external host would implement flow control using GPIOs-the large receive FIFO allows the external UART to enable its up to 16-byte transmitter FIFO without causing an overrun in the Hammerhead.)

- Fixed 8N1 operation (8 data bits, no parity, 1 stop bit)

- False start bit, framing error, and overrun detection.

- Supports bussed UART mode via a chip select pin see Chapter 2.1.6 and Chapter 5.9.1

## 2.1.1 Baud Rate Generator

After the Hammerhead is brought out of reset, the baud rate generator requires a series of synchronization (0x80) characters to be sent from the host to determine the baud rate. Bytes can be sent with either zero idle time or infinite idle time between them. This enables the Hammerhead to match the host's baud rate, and gives the host the flexibility to use any baud rate regardless of the reference clock frequency.

The baud rate generator provides the bit period clock, baud rate clock, to both the receiver and transmitter logic. The generated clock frequency is 16 times the baud rate to enable the receiver logic to perform accurate bit sampling.

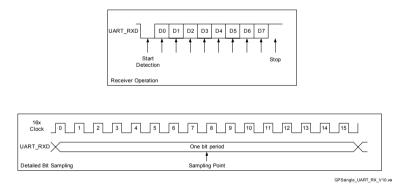

## 2.1.2 Asynchronous Receiver

The UART\_RXD pin is connected to a digital noise filter which removes short glitches up to 1/16<sup>th</sup> of the bit period from the received data signal.

The UART detects the start of a received character by sampling the UART\_RXD pin until it receives a valid start bit. A valid start bit is defined as a low level (space) on the

#### Host Interfaces

UART\_RXD pin which has a duration of at least 1/2 (8/16<sup>th</sup>) of the bit period. Spaces which are less than 1/2 of the bit period are ignored.

After a valid start bit is detected, the receiver samples at the assumed mid-point of every subsequent bit. (There will be up to 1/16<sup>th</sup> of a bit period initial phase error due to the 16X sampling clock rate, and a cumulative error which depends on the difference between the baud clock of the external transmitter and the Hammerhead receiver.)

If a character is received with an invalid stop bit (stop is sampled at a low level) then a framing error is generated. This information is provided to the UART interface. Note that if a break condition is present on UART\_RXD pin, the Hammerhead will detect it as a framing error. If this occurs in the middle of a packet it will result in that packet being discarded, and if it occurs between packets the UART interface will ignore it.

After a character is received it is written to the receiver FIFO. If the receiver FIFO is full, then an overrun condition is recorded and made available to the UART interface. In normal operation the hardware flow control will prevent overruns from occurring.

The actual point at which UART\_RXD is sampled is based on the 16X baud clock.

## Figure 2-1 UART Reception

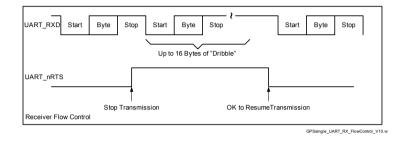

2.1.3 Receiver Flow Control

When the Hammerhead is ready to receive data, the UART\_nRTS (ready for receiving) pin will be asserted low. The external host may send data to the Hammerhead whenever UART\_nRTS is asserted, provided that the UART has been properly initialized. When the Hammerhead cannot keep up with the incoming data, it de-asserts the UART\_nRTS pin by raising it to the high state. The external host is allowed to send up to 16 additional bytes after UART\_nRTS is de-asserted. This is allowed because the external host may not recognize the de-assertion of UART\_nRTS immediately, and may have loaded up to

#### **Host Interfaces**

16 bytes in its transmitter FIFO (the host's transmitter FIFO may not understand hardware flow control).

## Figure 2-2 UART Receiver Flow Control

# 2.1.4 Asynchronous Transmitter

The transmitter transmits characters as they become available in the transmitter FIFO. The transmitter uses the 8N1 format which was previously shown for the asynchronous receiver. The transmitter can be disabled by the hardware flow control logic if the external host cannot keep up with the data rate.

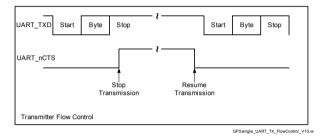

## 2.1.5 Transmitter Flow Control

Before transmitting a character, the transmitter state machine checks the state of the UART\_nCTS pin. When UART\_nCTS is asserted (low) by the host, the Hammerhead UART transmitter will send out a character whenever one is available. When UART\_nCTS is de-asserted by the external host, the Hammerhead will not transmit any characters (if UART\_nCTS is de-asserted in the middle of a character transmission, the UART transmitter will complete the transmission of that character before idling). Depending on the timing of UART\_nCTS versus the Hammerhead internal clocks, one additional character may be transmitted after UART\_nCTS is de-asserted. As long as

#### Host Interfaces

UART\_nCTS is de-asserted by the middle of the STOP bit, then no additional characters will be transmitted.

## Figure 2-3 UART Transmitter Flow Control

## Table 2-2Transmit pacing register

| Register          | Description                                                                                    |

|-------------------|------------------------------------------------------------------------------------------------|

| TX<br>pacing[7:0] | UART transmit pacing-controls the number of idle bits inserted between transmitted characters. |

|                   | Effectivetxbaudrate = $\frac{10}{10 + TXpacing} \cdot baudrate$                                |

|                   | Reset Value =8'h00                                                                             |

## 2.1.6 UART Chip Select

The UART interface is designed so that one host UART is able to communicate with multiple peripherals. This is achieved by the following:

• When OMS[2:0] is in the state [11x], i.e. the UART interface is being used then the OMS0 pin acts as an active high UARTCS. If the UART chip select feature is not needed, then this pin is coupled high.

When UARTCS is asserted high, then the UART behaves normally.

When UARTCS is de-asserted low, then the UART is not selected. The behaviour of the UART is modified as follows:

- TX the TX line is tri-stated so that it may be shared with other UARTs.

- UART\_nCTS the UART\_nCTS pin is ignored. It is treated as if it were de-asserted, so the UART transmitter will be disabled.

#### Host Interfaces

- UART\_RX the UART\_RX line is ignored. Internally it is treated as if it were idle so that any serial activity directed to another UART will be ignored.

- UART\_nRTS the UART\_nRTS line is tri-stated so that it may be shared with other UARTs.

## 2.2 SPI Host Interface

The SPI bus is a full duplex, synchronous interface.

The Hammerhead provides an industry standard SPI interface for use with hosts which contain a hardware SPI controller. It provides the following features:

- The maximum datarate is that the SPI interface supports is dependent on the reference clock, CLK, according to the formula: ( $F_{CLK}/10)Mbps$ , where  $F_{CLK}$  is the Reference clock frequency in MHz

- Support of SPI mode 0 (CPOL=0, CPHA=0)

- Support of normal SPI bit ordering (MSB first)

- Optional interrupt generation when the host needs to service the SPI slave.

The Hammerhead only performs transfers that are a multiple of 8 bits.

For a description of the SPI timing see Chapter 5.9.3

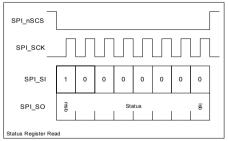

## 2.2.1 SPI Cycles

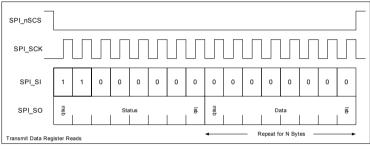

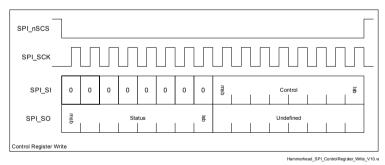

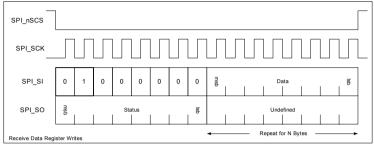

The four supported transfer types are shown in the following four figures using a simplified notation.

## Figure 2-4 SPI Status Register (Read)

Hammerhead\_SPI\_StatusRegister\_Read\_V10.vs

#### Host Interfaces

Note: The status register read is shown for completeness. Because all of the operations begin with a status register read, it is not expected that a status register read will be performed as an isolated SPI bus event.

Hammerhead\_SPI\_TransmitDataRegister\_Reads\_V10.vs

## Figure 2-6 SPI Control Register (Write)

Product Specification

#### **Host Interfaces**

## Confidential

## Figure 2-7 SPI Receive Data Register (Writes)

Hammerhead\_SPI\_ReceiveDataRegister\_Whites\_V10.vs

## Confidential

## Host Interfaces

# 2.3 I<sup>2</sup>C Host Interface

The I<sup>2</sup>C interface comprises the following features:

- Slave-only operation (slave transmitter and slave receiver).

- 7-bit device address.

- Supports standard (up to 100 kbit/s) and fast (up to 400 kbit/s) modes.

- Optional interrupt generation when the host needs to service the I<sup>2</sup>C slave.

- Slave never stretches the I<sup>2</sup>C\_SCL low period.

For the I<sup>2</sup>C timing see Chapter 5.9.2.

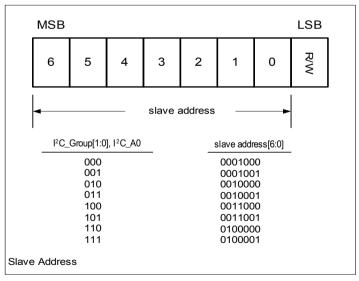

# 2.3.1 I<sup>2</sup>C Slave Address

The Hammerhead slave address is determined by the state of the  $I^2C\_GROUP[1:0]$  and  $I^2C\_A0$  pins. The Hammerhead will ignore any address except for its assigned slave address. Addresses outside of this range, including the general call address, START byte, CBUS address, reserved addresses, Hs-mode master code, and 10-bit slave addressing are ignored.

## Figure 2-8 I<sup>2</sup>C Slave Address

Hammerhead\_I2C\_SlaveAddress\_V10.vsd

#### Host Interfaces

# 2.3.2 I<sup>2</sup>C Read/Write Cycles

The four supported transfer types are shown in the following four figures.

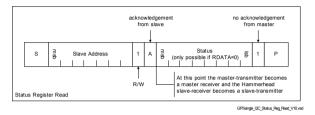

## Figure 2-9 I<sup>2</sup>C Status Register (Read)

## Figure 2-10 I<sup>2</sup>C Transmit Data Register (Reads)

Note: Note that the data register reads are only preceded by a status register read if the RDATA control bit is cleared to zero, see **Figure 2-13**. Normally RDATA should be left cleared to zero as this behaviour is useful since software makes use of the

#### **Host Interfaces**

status register read to determine how much data is available. Set RDATA to one only when required for operation with certain limited I2C masters.

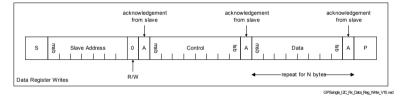

## Figure 2-11 I<sup>2</sup>C Control Register (Write)

Figure 2-12 I<sup>2</sup>C Receive Data Register (Writes)

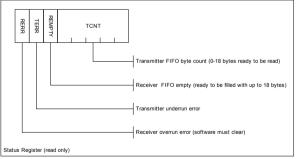

# 2.4 Status, Control, and Data Registers

The SPI and I<sup>2</sup>C serial interfaces contain status, control, and data registers which are used to send and receive data to the Hammerhead. The software is responsible for

#### Confidential

#### **Host Interfaces**

avoiding data underruns and overruns. This is done by monitoring the REMPTY and TCNT fields in the status register.

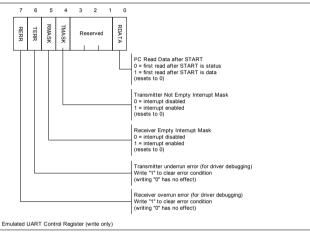

#### Figure 2-13 Hammerhead Control Register (Write)

Hammerhead\_ControlRegister\_Write\_V10.vsd

Figure 2-14 Hammerhead Status Register (Read)

Hammerhead\_StatusRegister\_Read\_V10.vsd

#### **Host Interfaces**

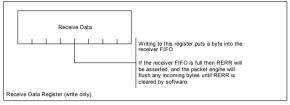

Hammerhead\_ReceiveDataRegister\_Write\_V10.vsd

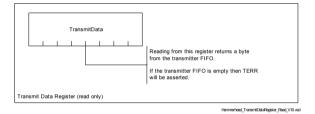

## Figure 2-16 Hammerhead Transmit Data Register (Read)

## 2.5 nINTR

## 2.5.1 I<sup>2</sup>C and SPI

For the I<sup>2</sup>C and SPI interfaces the nINTR generation is controlled by the RMASK and TMASK in the control register. Software can use the TMASK (transmitter not empty interrupt mask) to detect when data is available to be read from the Hammerhead. This way software does not need to spend time polling the status register when the Hammerhead is active. The RMASK (receiver empty interrupt mask) bit can be used in the unlikely case that the Hammerhead isn't able to process data as fast as the host can transmit it.

## 2.5.2 UART

The nINTR signal allows the host to sleep during long integrations. Consequently it may not be able to receive serial data during this time. The Hammerhead uses this signal to wake-up the host before transmitting any data.

This is implemented as follows:

- The host transmits a packet to the Hammerhead telling it to enter SLEEP mode.

- The interrupt line nINTR will be asserted (low) whenever the UART is in SLEEP mode and there are characters in the UART transmit FIFO ready to be sent to the host.

#### Host Interfaces

- When the UART is in SLEEP mode then it will ignore any bytes transmitted by the host except for INTACK (interrupt acknowledge - 0xFA) and WAKE (0xFB). Also note that the host needs to leave nCTS asserted for the UART to be allowed to transmit any bytes. Therefore if nCTS is de-asserted when an INTACK byte is received, then the INTACK byte is ignored since its processing requires an interrupt status byte to be transmitted.

- When an INTACK byte is received and nCTS is asserted low, then the UART will transmit the interrupt status (0x7A = interrupt not asserted, 0x7B = interrupt asserted) and exit sleep mode only if the interrupt is currently asserted. (This behaviour facilitates sharing the interrupt with other peripherals.)

- When a WAKE byte is received, then the UART will exit sleep mode and will not transmit the interrupt status byte. This feature can be used to get the UART out of SLEEP mode.

The reason for not transmitting the interrupt status in response to receiving the WAKE byte is that this makes the software design easier in a system which uses a dedicated interrupt pin for the Hammerhead. Since the software is then able to acknowledge all interrupts with WAKE, knowing that all the interrupts are coming from the Hammerhead, without needing to check the interrupt status, this simplifies the UART receiver code - every incoming byte is a data byte.

When the UART is in SLEEP mode, it will not transmit any bytes unless instructed to do so by the host.

System Clocks description

# 3 System Clocks description

## 3.1 Overview

The Hammerhead supports a wide variety of clock schemes. There are four clock interfaces of which two are mandatory, the Reference clock, CLK and RTCCLK

The RTCCLK is used to clock the standby timer in low power modes and thus is required for low power operation.

The SYNC signal input is used if GPS timing is already available in the system; this is used to develop a relationship between the GPS timing and the Reference clock (CLK) in the Hammerhead.

The CNTIN is an external high frequency reference clock input which can be derived from network timing in for instance GSM systems.

## 3.2 Reference clock

The Hammerhead makes use of an external reference clock signal, 10-40MHz, provided by the host system, as shown in **Figure 1-6**, or a standalone TCXO, as shown in **Figure 1-9**. The Internal  $\Sigma\Delta$  Clock PLL is driven from this clock, and provides the master clock used for the correlator blocks. A wide range of reference clocks can be used, due to the PLLs flexible fractional-N divider. The reference clock is set, based on user-defined constants in the driver software on the host, and can be tailored to a specific system frequency plan.

The clock input contains an amplifier (ICA) to enable the use of an analog clock. The clock mode, analog or digital, is configureable by software.

## 3.2.1 UART, SPI and I2C interfaces

The UART, SPI and I<sup>2</sup>C interfaces are not driven by the PLL. These interfaces use the external reference clock directly. This makes it possible for the software to power down or change settings of the PLL, while the interfaces still are accessible.

## 3.3 SYNC clock

The SYNC clock is used in systems which are synchronized to an external source of GPS time. In such designs, a precise digital synchronization signal (SYNC) is input to the chip so that this counter can measure the time difference between GPS timing and the internal clock. The measurement data is used by the navigation control software to establish a precise relationship between the Hammerhead internal clocks and the external time source.

System Clocks description

#### Confidential

## 3.4 CNTIN clock

The CNTIN clock provides a means for measuring the reference frequency (CLK) relative to a separate, high-accuracy external digital reference signal (CNTIN).

## 3.5 RTCCLK

The RTCCLK is a 32.768kHz digital clock. This clock can be used in Power Down Mode, see **Table 4-2**. The Hammerhead maintains GPS time by using the RTCLK when the CLK is unavailable and is mandatory for low power operations. RTCCLK is also used to exit reset.

#### **Power Management**

## 4 **Power Management**

## 4.1 Power Supplies and Voltage Regulators

Power to the Hammerhead device can be supplied from:

- The internal voltage regulators

- External regulated voltage supplies

- A combination of the above

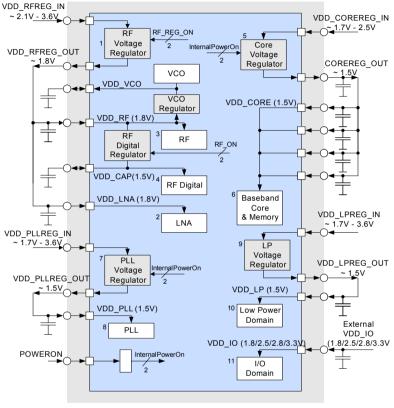

#### 4.1.1 Internal voltage regulators.

If an internal voltage regulator is being used, the regulator output must be connected to the corresonding Vdd input. If the regulator is not used it is left unconnected.

See Figure 4-1 for a complete illustration.

The internal regulators are controlled by the host software, except the LP voltage regulator which is always enabled.

#### **Power Management**

#### Figure 4-1 Voltage regulators being used to supply the voltage domains.

All Internal Voltage Regulators in Use

GPSsingle\_Voltage\_Regulators\_v10.vsd

See Table 5-11 for decoupling values.

Note: The VDD\_CAP and VDD\_VCO pins are only available for decoupling purposes. No current should be forced in or extracted from these pins

## 4.1.2 External regulated voltage supplies.

The External Regulators must be switched on and off by the external host.

#### **Power Management**

## 4.1.3 A combination of the above.

Any combination of internal and external regulators can be used depending on the supplies available in the host system.

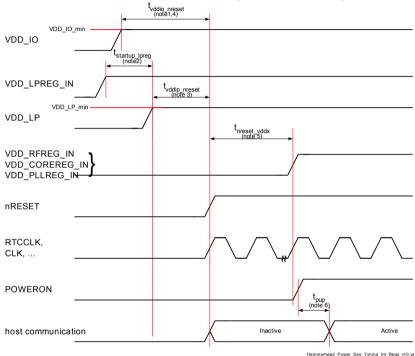

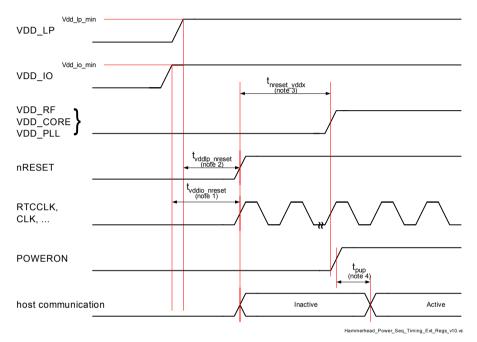

## 4.2 Power Up and Power Down Sequencing

In order to avoid problems with ESD or outputs being forced into the wrong state(s) the following sequences should be adhered to when powering up or powering down the Hammerhead. See **Figure 4-2** or **Figure 4-3**

## 4.2.1 Power Up Sequence

The following sequence should be used for "Powering Up" the Hammerhead when using the nRESET:

- Make sure no interfacing signals are driving current into the device. nRESET must be asserted (low) and POWERON must be de-asserted (low).

- Apply VDD\_IO and VDD\_LP, alternatively VDD\_LPREG\_IN.

- After VDD\_IO has been stable for t<sub>vddio\_nreset</sub>, see Table 4-1, and VDD\_LP has been stable for t<sub>vddip\_nreset</sub>, see Table 4-1, de-assert nRESET (high).

Hammerhead is now in Power Down Mode, according to Table 4-2.

- Apply VDD\_CORE alternatively VDD\_COREREG\_IN, VDD\_PLL alternatively VDD\_PLLREG\_IN and VDD\_RFREG\_IN alternatively VDD\_RF

- Assert pin POWERON (high) This enables the CORE and PLL regulators (if used). Hammerhead is now in Software Only Standby.

- After 1 ms, the power supplies will be stable.

- After the reset sequence is complete the host can communicate through the serial interface.

## 4.2.2 Power Down Sequence

The following sequence should be used for "Powering Down" the Hammerhead:

- From Software Only Standby mode, de-assert the POWERON pin. This disables the CORE and PLL regulators (if used). The Hammerhead is now in Low Power Standby or Power Down Mode, see Table 4-2.

- Make sure no interfacing signals are driving current into the device.

- Remove VDD\_CORE alternatively VDD\_COREREG\_IN, VDD\_PLL alternatively VDD\_PLLREG\_IN and VDD\_RFREG\_IN alternatively VDD\_RF

- Remove VDD\_IO and VDD\_LP alternatively VDD\_LPREG\_IN. The device is now completely powered off

#### **Power Management**

## Figure 4-2 Hammerhead Power Up Sequencing with Internal Regulators.

Hammerhead Power Up Sequencing with Internal Regulators

- Note: 1: Delay from VDD\_IO to nRESET or any digital input signal set high  $\geq t_{vddio}$ <sub>nreset</sub> to minimize current consumption during initial power sequencing.

- Note: 2: VDD\_LPREG\_IN should be applied t<sub>startup\_lpreg</sub> before VDD\_LP min is required.

- Note: 3: nRESET must remain asserted for  $t_{vddlp\_nreset}$  after VDD\_LP is within limits to guarantee that the chip is set up correctly.

- *Note: 4: Delay from VDD\_IO to any digital signal input high must be >=0 and should be greater than*  $t_{vddio\_nreset}$  *to minimize current consumption during initial power sequencing.*

- *Note:* 5: $t_{nreset vddx}$  should be > 0 before POWERON is asserted.

- Note: 6:Delay from POWERON to nReset\_core de-asserted. Programmable from 1.9-15.6ms. Bus interface will not accept transfers until  $t_{pup}$  has been met. POWERON is controlled by software.

#### **Power Management**

#### Figure 4-3 Hammerhead Power Up Sequencing with External Regulators.

Hammerhead Power Up Sequencing with External Regulators

- Note: 1:Delay from VDD\_IO to nRESET or any digital input signal set high >= t<sub>vddio\_nreset</sub> to minimize current consumption during initial power sequencing.

- Note: 2:nRESET must remain asserted for t<sub>vddlp\_nreset</sub> after VDD\_LP is within limits to guarantee proper chip initialization.

- Note: 3:Delay from VDD\_IO to any digital signal input high must be >=0 and should be greater than  $t_{pw_nreset}$  to minimize current consumption during initial power sequencing.

- Note: 4:Delay from POWERON to nReset\_core de-asserted.Programmable from 1.9-15.6ms. Bus interface will not accept transfers until  $t_{pup}$  has been met. POWERON is controlled by software

## **Power Management**

| Table 4-1                  | Power sec              | Power sequencing parameters                                     |  |  |  |  |  |  |  |

|----------------------------|------------------------|-----------------------------------------------------------------|--|--|--|--|--|--|--|

| Parameter                  | arameter Value Comment |                                                                 |  |  |  |  |  |  |  |

| t <sub>vddio_nreset</sub>  | >500ns                 | This to ensure that no unnecessary current is drawn             |  |  |  |  |  |  |  |

| t <sub>startup_lpreg</sub> | >1ms                   | See Table 5-12 "Regulator Limits (Dynamic)" on Page 54          |  |  |  |  |  |  |  |

| t <sub>vddlp_nreset</sub>  | >50ns                  | Allowing the control signals to be settled to the IO pads       |  |  |  |  |  |  |  |

| t <sub>nreset_vddx</sub>   | >500ns                 | This to ensure that no unnecessary current is drawn             |  |  |  |  |  |  |  |

| t <sub>pup</sub>           | 1.9-<br>15.6ms         | Programmable delay from POWERON until circuit fully functional. |  |  |  |  |  |  |  |

## Table 4-1 Power sequencing parameters

#### **Power Management**

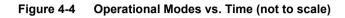

#### 4.3 Power Modes

The Hammerhead device supports three operational modes and three standby modes. These are defined in **Section 4.3.1** to **Section 4.3.6** below.

| Mode                        | Conditions                                                               | Function                                                                                       | CLK | RTCLK | Control                        |

|-----------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|-------|--------------------------------|

| Full<br>Processing          | All supply voltages and<br>clocks are applied                            | This gives the peak performance<br>with respect to TTFF. Core<br>frequency normal              | ON  | ON    | Software<br>POWERON<br>pin =1  |

| Reduced<br>Processing       | All supply voltages and<br>clocks are applied                            | This reduces the peak current<br>required but also gives longer<br>TTFF Core frequency reduced | ON  | ON    |                                |

| Software<br>Only<br>Standby | All supply voltages and<br>clocks are applied                            | RF frontend off and Correlator<br>clock off.<br>Core frequency either normal or<br>reduced     | ON  | ON    |                                |

| Low Power<br>Standby        | Only VDD_LP and<br>VDD_IO supplies are<br>applied Reference clock<br>on  | No correlations active and core<br>and PLL turned off. Time is kept<br>with RTCCLK             | OFF | ON    | Software,<br>POWERON<br>pin =0 |

| Power<br>Down               | Only VDD_LP and<br>VDD_IO supplies are<br>applied Reference clock<br>off |                                                                                                |     | ON    |                                |

| IC off                      | All supplies off                                                         | No activity and no data saved                                                                  | OFF | OFF   |                                |

## 4.3.1 Full Processing Mode

The device is fully active.

- All supply voltages and clocks are applied.

- Correlators are running at 72 MHz. This is the mode that gives peak performance with respect to TTFF and energy usage.

#### 4.3.2 Reduced Processing Mode

The device is fully active.

- All supply voltages and clocks are applied.

- Correlators are running at 48MHz. This mode is used to reduce the peak current required by the VDD\_CORE supply. It can be used if the system power supply device(s) have current limitations. The host software chooses this mode.

In both the above processing modes dynamic power saving occurs automatically. After a correlator has acquired sufficient data for a fix, the clocks to that correlator are internally disabled.

#### **Power Management**

If no correlations are taking place, the hardware can automatically turn off parts of the RF block.

## 4.3.3 Software Only Standby

No correlations are taking place

- The RF Front-end is turned off, either by disabling the RF circuitry, disabling the RF voltage regulator, or externally switching the RF supply off. (Depending on Platform Application)

- · The clocks to the correlators are turned off.

The rest of the device is fully active

## 4.3.4 Low Power Standby

No correlations are taking place and the core is turned off.

- Only the VDD\_LP and the VDD\_IO voltage supplies are applied.

- The Standby Counter is clocked with RTCCLK.

#### 4.3.5 Power Down

No correlations are taking place and the core is turned off.

- Only the VDD\_LP and the VDD\_IO voltage supplies are applied.

- RTCCLK, 32.768kHz, must be on to exit reset.

- · No time keeping in Power Down mode

## 4.3.6 IC Off

- · All supplies to the IC are off.

- No Voltages on any of the I/Os

If a bus architecture is being used on the platform, this mode cannot be used as signal voltages may be present on the interface inputs.

**Power Management**

Confidential

**Electrical Characteristics**

# 5 Electrical Characteristics

## 5.1 Absolute Maximum Ratings

#### Table 5-1Absolute Maximum Ratings.

| Parameter                             | Limit | Values | Unit | Notes             |

|---------------------------------------|-------|--------|------|-------------------|

|                                       | min.  | max.   |      |                   |

| Storage temperature                   | -55   | 150    | °C   |                   |

| RF Regulator input voltage            | -0.9  | 4.0    | V    | VDD_RFREG_IN      |

| RF Regulator output voltage           | -0.9  | 4.0    | V    | VDD_RFREG_OUT     |

| RF Supply voltages                    | -0.9  | 4.0    | V    | VDD_LNA<br>VDD_RF |

| Voltage on any RF pin                 | -0.9  | 4.0    | V    |                   |